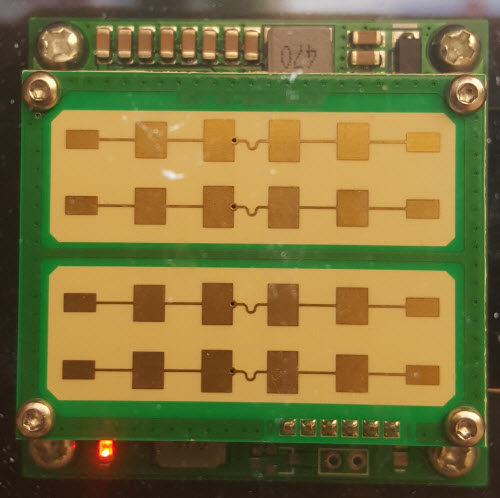

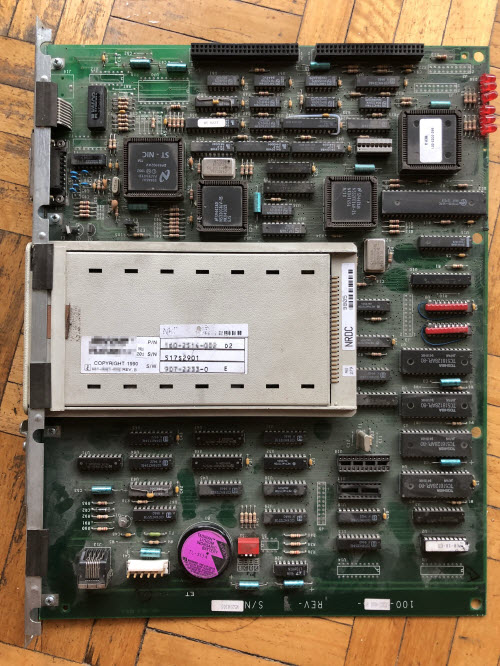

The Ware for September 2018 is shown below.

Been a busy month banging my head against the wall of getting FCC/CE certification for NeTV2, and spending thousands of dollars on dozens of tests — more time, effort, and treasure than developing the product itself. This is my least favorite aspect of product development — the regulatory burdens are just so immense if you actually try to comply with all the rules, especially with such a global marketplace (every region you legally serve multiplies your paperwork load, not to mention different SKUs for power supplies & manual/packaging translations).

Rather ironic to have finally figured out all the technical tricks to make production in small batches efficient, only to find there’s no efficient way to deal with regulatory hurdles. It’s a discouraging message for small-time makers and innovators, and tilts things in the favor of large corporations with the funding and scale to build internal certification teams and facilities to make the regulatory process efficient and predictable.